多速率FIR滤波器 |

您所在的位置:网站首页 › fpga 数字滤波器 › 多速率FIR滤波器 |

多速率FIR滤波器

|

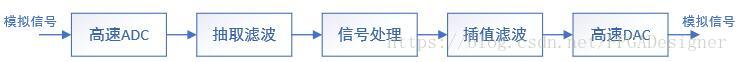

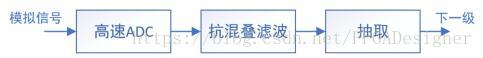

该篇是FPGA数字信号处理的第15篇,选题为多速率信号处理系统中用到的多速率FIR滤波器。本文将简单介绍多速率信号处理系统的基本概念,以及使用Quartus和Vivado的IP核设计多速率FIR滤波器的方法。 多速率信号处理这个概念是相对于单速率(Single Rate)信号处理而言的。单速率是指整个信号处理流程中只有一种数据速率;多速率是指系统中存在多个数据速率。使用多速率信号处理可以节省存储空间、减少通信数据量、减少运算量、减轻设计难度。 比如在DDC(数字下变频)系统中,前级需要很高的采样率fs确保ADC采集到信号的信噪比;而在去载波并提取出低频的基带信号后,信号有效带宽已经很小,此时可以满足要求的采样率也远远低于fs,如果不进行数据速率转换的处理,会造成许多资源的浪费和设计上的困难(详情参考“FPGA综合系统设计(七):基于DDC的两路信号相位差检测: https://blog.csdn.net/FPGADesigner/article/details/80785174”)。 一个简单的多速率信号处理系统框图如下所示: 多速率FIR滤波器其实已经在上面链接中的设计用到过,本文再结合概念单独总结一下。后面的文章将介绍CIC滤波器和HB滤波器的设计。 抽取与内插当需要降低采样率时,输入信号数据每隔D-1个取一个,取出的数据依次排序,这个过程称作D倍抽取,采样率变为原来的1/D。但是我们需要确保抽取之后的采样率仍然可以满足Nyquist采样定理,否则会造成频谱的混叠。当然由于ADC的转换也会在整个频段内引入白噪声,因此在抽取前还是需要加入抗混叠滤波器。如下图所示: MATLAB中的语法可以很简单的实现抽取和插值操作。抽取过程如下: t = 0 : 1 / Fs : 0.5; c = 2 * pi * f * t; si=sin(c); %产生正弦波 D=8; %抽取倍数 d2 = si(1 : D : length(t)); %抽取 12345插值过程如下: t = 0 : 1/Fs : 0.5; c = 2 * pi * f * t; si = sin(c); %产生正弦波 I=8; %内插倍数 Isi = zeros(1, length(si)*I); %先构造全0序列 Isi(1 : I : length(Isi)) = si; %将源信号插入 123456滤波器的设计不再赘述。 FPGA设计Quartus和Vivado的FIR IP核都可以设置为多速率FIR模式,完成数据速率的转换工作。比如在上文链接内的设计中,ADC需要以100MHz的速率采集20MHz的信号,通过DDC解调后基带信号频率仅有500kHz。将FIR设置为10倍抽取模式,采样率降为10MHz,足以完成接下来的处理。 Quartus中以FIR Compiler IP核为例: Vivado中以FIR Compiler IP核的7.2版本为例: |

【本文地址】

今日新闻 |

推荐新闻 |

多速率信号处理主要包括数据速率的转换和LPF的设计两个过程。数据速率的转换包括抽取(Decimation,降低采样率)和内插(interpolation,提高采样率)。抽取/内插时应保证信号的有效频带内没有频谱混叠,因此需要完成LPF的设计,常用的有多速率FIR滤波器、CIC滤波器、HB滤波器。

多速率信号处理主要包括数据速率的转换和LPF的设计两个过程。数据速率的转换包括抽取(Decimation,降低采样率)和内插(interpolation,提高采样率)。抽取/内插时应保证信号的有效频带内没有频谱混叠,因此需要完成LPF的设计,常用的有多速率FIR滤波器、CIC滤波器、HB滤波器。 当需要提高采样率时,在两个相邻的数据之间插入I-1个零值,再进行低通滤波,这个过程称作I倍内插,采样率变为原来的I倍。只要LPF的通带为信号的有效带宽,即使插值时只插入零值点(没有插入采样值的点),也可以达到I倍内插的效果。经过插值后的信号由DAC输出会引入更小的高频噪声。如下图所示:

当需要提高采样率时,在两个相邻的数据之间插入I-1个零值,再进行低通滤波,这个过程称作I倍内插,采样率变为原来的I倍。只要LPF的通带为信号的有效带宽,即使插值时只插入零值点(没有插入采样值的点),也可以达到I倍内插的效果。经过插值后的信号由DAC输出会引入更小的高频噪声。如下图所示:  上面抽取和内插实现的都是整数倍数据速率的转换。而实际设计中遇到的更多不会是整数倍关系。可以使用先内插、再抽取的方式完成采样率为有理数比值的数据速率转换,且可以共用一个LPF,截止频率选取二者的最小带宽即可。如下图所示:

上面抽取和内插实现的都是整数倍数据速率的转换。而实际设计中遇到的更多不会是整数倍关系。可以使用先内插、再抽取的方式完成采样率为有理数比值的数据速率转换,且可以共用一个LPF,截止频率选取二者的最小带宽即可。如下图所示:

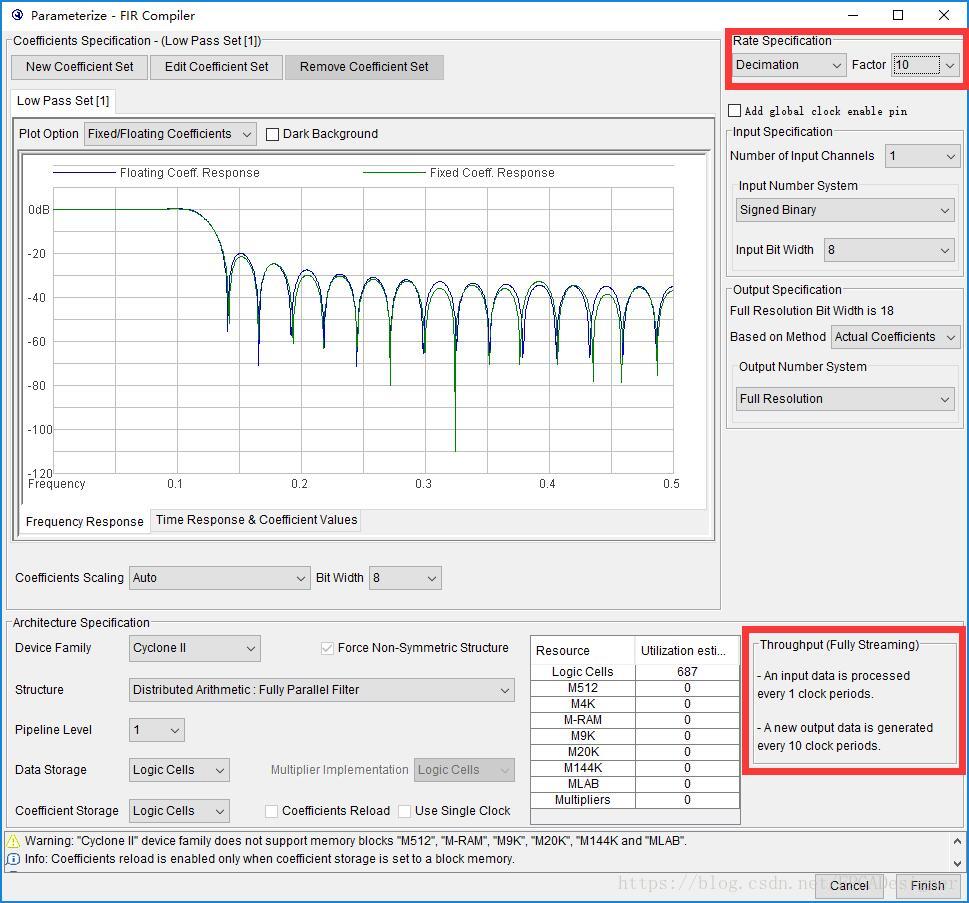

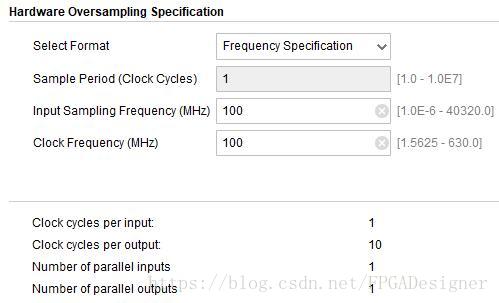

右上角的Rate Specification即为设置内插或抽取,Factor表示抽取和内插 的倍数。设置好后,在右下角的Throughput中可以看到输入数据速率和输出数据速率。此处设置为了10倍抽取,则每10个时钟才会输出一个有效数据,相当于采样率降低了10倍。

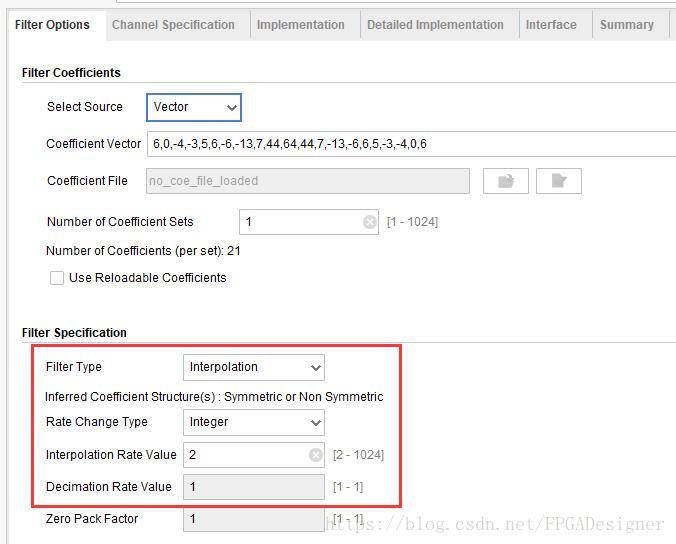

右上角的Rate Specification即为设置内插或抽取,Factor表示抽取和内插 的倍数。设置好后,在右下角的Throughput中可以看到输入数据速率和输出数据速率。此处设置为了10倍抽取,则每10个时钟才会输出一个有效数据,相当于采样率降低了10倍。 在Filter Options标签下,“Filter Type”可以设置为抽取或内插模式,并设置对应的倍数Decimation Rate Value和Interpolation Rate Value。在Channel Specification标签下设置好输入采样速率和时钟频率后,可以看到输入数据速率和输出数据速率(这里设置了10倍抽取)。

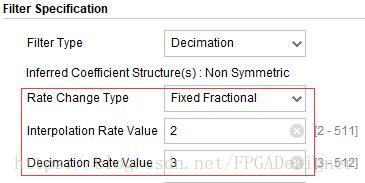

在Filter Options标签下,“Filter Type”可以设置为抽取或内插模式,并设置对应的倍数Decimation Rate Value和Interpolation Rate Value。在Channel Specification标签下设置好输入采样速率和时钟频率后,可以看到输入数据速率和输出数据速率(这里设置了10倍抽取)。  此外Vivado的FIR IP核还提供了非整数倍抽取/内插的功能,将“Rate Change Type”修改为“Fixed Fractional”,即可分别设置插值倍数和抽取倍数,组合为一个值为有理数的倍数,如下图所示:

此外Vivado的FIR IP核还提供了非整数倍抽取/内插的功能,将“Rate Change Type”修改为“Fixed Fractional”,即可分别设置插值倍数和抽取倍数,组合为一个值为有理数的倍数,如下图所示:  可以看出多速率FIR滤波器必须工作在很高的频率上(即数据转换速率前后的两个采样率中更大的那个速率),才能完成数据速率转换的工作。而FIR通常会使用大量的乘法器,因此具有占用资源多的缺点。与之相比,CIC滤波器和HB滤波器在结构和性能上更优良,将在后面的文章中介绍。

可以看出多速率FIR滤波器必须工作在很高的频率上(即数据转换速率前后的两个采样率中更大的那个速率),才能完成数据速率转换的工作。而FIR通常会使用大量的乘法器,因此具有占用资源多的缺点。与之相比,CIC滤波器和HB滤波器在结构和性能上更优良,将在后面的文章中介绍。